aritmetika_dasar

Transcript of aritmetika_dasar

-

8/9/2019 aritmetika_dasar

1/8

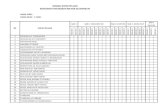

PETUNJUK PRAKTIKUM ELEKTRONIKA DIGITAL 1

PERCOBAAN 8.

RANGKAIAN ARITMETIKA DIGITAL DASAR

UUUUTUJUAN:

Setelah menyelesaikan percobaan ini mahasiswa diharapkan mampu

Memahami rangkaian aritmetika digital : adderdansubtractor

Mendisain rangkaian adder dan subtractor (Half dan Full)

berdasarkan Tabel Kebenaran yang diketahui

UUUUPERALATAN:

1. Logic Circuit Trainer ITF-02 / DL-02

2. Oscilloscope

UUUUTEORI:

Rangkaian aritmetika digital dasar terdiri dari dua macam : Adder, atau

rangkaian penjumlah, berfungsi menjumlahkan dua buah bilangan yang telah

dikonversikan menjadi bilangan-bilangan biner, dan Subtraktor, atau rangkaian

pengurang, yang berfungsi mengurangkan dua buah bilangan.

UUUU1. HALF ADDER

Sebuah rangkaian Adder terdiri dari Half Adderdan Full Adder. Half Adder

menjumlahkan dua buah bit input, dan menghasilkan nilai jumlahan (sum) dan nilai

lebihnya (carry-out). Half Adderdiletakkan sebagai penjumlah dari bit-bit terendah

(Least Significant Bit). Blok Diagram dari sebuah rangkaian Half Adderditunjukkan

pada gambar 8-1.

PERCOBAAN 8.Halaman 36RANGKAIAN ARITMETIKA DIGITAL DASAR

-

8/9/2019 aritmetika_dasar

2/8

PETUNJUK PRAKTIKUM ELEKTRONIKA DIGITAL 1

Gambar 8-1. Blok DiagramHalf Adder

Prinsip kerjaHalf Adderditunjukkan pada gambar 8-2.

Gambar 8-2. Prinsip KerjaHalf Adder

SebuahHalf Addermempunyai Tabel Kebenaran seperti pada Tabel 8-1.

Tabel 8-1. Tabel Kebenaran Half Adder

PERCOBAAN 8.Halaman 37RANGKAIAN ARITMETIKA DIGITAL DASAR

Half

Adder

A

B

CBO

B

INP

UT

OU

TP

UT

Cin Cin

A1 A0

+ B1 B0

2 1 0

+ +

Cout Cout

A0 B0 0 Cout0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

-

8/9/2019 aritmetika_dasar

3/8

PETUNJUK PRAKTIKUM ELEKTRONIKA DIGITAL 1

Berdasarkan output-output yang didapatkan dari Tabel Kebenaran, dibuat rangkaian

seperti gambar 8-3.

Gambar 8-3. RangkaianHalf Adder

UUUU2. FULL ADDER

Sebuah Full Addermenjumlahkan dua bilangan yang telah dikonversikan

menjadi bilangan-bilangan biner. Masing-masing bit pada posisi yang sama saling

dijumlahkan. Full Addersebagai penjumlah pada bit-bit selain yang terendah. Full

Adder menjumlahkan dua bit input ditambah dengan nilai Carry-Out dari

penjumlahan bit sebelumnya. Output dari Full Adder adalah hasil penjumlahan (Sum)

dan bit kelebihannya (carry-out). Blok diagram dari sebuahfull adderdiberikan pada

gambar 8-4.

Gambar 8-4. Blok Diagram Full Adder

Tabel Kebenaran untuk sebuah Full Adderdiberikan pada Tabel 8-.2.

PERCOBAAN 8.Halaman 38RANGKAIAN ARITMETIKA DIGITAL DASAR

BBB0

BBB=ABBB

0BBBBBBB

0BBB+ABBB

0BBBBBBB

0BBB

ABBB0

BBB

BBBB0

BBB

CBBBOUT

BBB=ABBB

0BBBBBBB

0BBB

BBB0

BBB

=ABBB0

BBBBBBB

0BBB+ABBB

0BBBBBBB

0BBB

Full

Adder

A

B

CBBBO

BBB

CBBBIN

B

BB

INP

UT O

UTP

UT

-

8/9/2019 aritmetika_dasar

4/8

PETUNJUK PRAKTIKUM ELEKTRONIKA DIGITAL 1

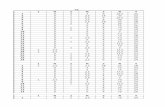

Tabel 8-2. Tabel Kebenaran Full Adder

Berdasarkan output-output yang didapatkan dari Tabel Kebenaran, dibuat rangkaian

seperti gambar 8-5.

Gambar 8-5. RangkaianFull Adder

PERCOBAAN 8.Halaman 39RANGKAIAN ARITMETIKA DIGITAL DASAR

A1 B1 CIN 1 Cou t0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

A1

B1

CIN

COUT

1

-

8/9/2019 aritmetika_dasar

5/8

PETUNJUK PRAKTIKUM ELEKTRONIKA DIGITAL 1

UUUU1. HALF SUBTRACTOR

Sebuah rangkaian Subtractorterdiri dariHalf SubtractordanFull Subtractor.

Half Subtractor mengurangkan dua buah bit input, dan menghasilkan nilai hasil

pengurangan (Remain) dan nilai yang dipinjam (Borrow-out). Half Subtractor

diletakkan sebagai pengurang dari bit-bit terendah ( Least Significant Bit). Blok

Diagram dari sebuah rangkaianHalf Subtractorditunjukkan pada gambar 8-6.

Gambar 8-6. Blok DiagramHalf Subtractor

Prinsip kerjaHalf Subtractor ditunjukkan pada gambar 8-7.

Gambar 8-7. Prinsip KerjaHalf Subtractor

Sebuah Half Subtractormempunyai Tabel Kebenaran seperti pada Tabel 8-3.

PERCOBAAN 8.Halaman 40RANGKAIAN ARITMETIKA DIGITAL DASAR

Half

Subtractor

A

B

R

BO

INP

UT O

UTP

UT

Bin Bin

A1 A0

- B1 B0

R1 R0

+ +

Bout Bout

-

8/9/2019 aritmetika_dasar

6/8

PETUNJUK PRAKTIKUM ELEKTRONIKA DIGITAL 1

Tabel 8-3. Tabel Kebenaran Half Subtractor

Berdasarkan output-output yang didapatkan dari Tabel Kebenaran, dibuat rangkaian

seperti gambar 8-8.

Gambar 8-8. RangkaianHalf Subtractor

UUUU4. FULL SUBTRACTOR

SebuahFull Subtractormengurangkan dua bilangan yang telah dikonversikan

menjadi bilangan-bilangan biner. Masing-masing bit pada posisi yang sama saling

dikurangkan.Full Subtractormengurangkan dua bit input dan nilai Borrow-Outdari

pengurangan bit sebelumnya Output dari Full Subtractoradalah hasil pengurangan(Remain) dan bit pinjamannya (borrow-out). Blok diagram dari sebuah full

subtractordiberikan pada gambar 8-9.

PERCOBAAN 8.Halaman 41RANGKAIAN ARITMETIKA DIGITAL DASAR

A0 B0 R0 Bout

0 0 0 0

0 1 1 1

1 0 1 0

1 1 0 0

A0

B0

R0

=A0B

0+A

0B

0

BOUT

=A0B

0

-

8/9/2019 aritmetika_dasar

7/8

PETUNJUK PRAKTIKUM ELEKTRONIKA DIGITAL 1

Gambar 8-.9. Blok DiagramFull Subtractor

Tabel Kebenaran untuk sebuah Full Subtractordiberikan pada Tabel 8-4.

Tabel 8-4. Tabel Kebenaran Full Subtractor

Berdasarkan output-output yang didapatkan dari Tabel Kebenaran, dibuat rangkaian

seperti gambar 8-10.

Gambar 8-10. RangkaianFull Subtractor

PERCOBAAN 8.Halaman 42RANGKAIAN ARITMETIKA DIGITAL DASAR

FullSubtractor

A

B

R

BBBBO

BBB

BBBBIN

BBB

IN

P

UT O

UTP

U

T

A1 B1 BIN R1 Bou t

0 0 0 0 0

0 0 1 1 1

0 1 0 1 1

0 1 1 0 1

1 0 0 1 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 1

A1

BBBB

1BBB

BBBBIN

B

BB

RBBB1

BBB

BBBB

OUTBBB

-

8/9/2019 aritmetika_dasar

8/8

PETUNJUK PRAKTIKUM ELEKTRONIKA DIGITAL 1

UUUUPROSEDUR :

1. Menggunakan Trainer ITF-02 atau DL-02, implementasikan rangkaian Half

Adder, seperti pada gambar 8-3. Buat Tabel Kebenarannya.

2. Seperti pada prosedur 1, implementasikan rangkaianFull Adder, seperti gambar

8-5. Buat Tabel Kebenarannya.

3. Seperti prosedur 1, implementasikan rangkaian Half Subtractor, seperti gambar

8-8. Buat Tabel Kebenarannya.

4. Seperti prosedur 1, implementasikan rangkaian Full Subtractor, seperti gambar

8-10. Buat Tabel Kebenarannya.

UUUUTUGAS :

1. Dengan menggunakan Tabel Kebenaran yang telah didapatkan dari percobaan,

buat K-map untuk masing-masing Rangkaian Aritmetika (Half Adder, Full adder,

Half Subtractor dan Full Subtractor). Dari K-map, dapatkan persamaan

sederhananya. Kemudian gambarkan rangkaiannya, sesuai dengan persamaan

yang didapat. Bandingkan hasilnya dengan rangkaian awal (yang anda rangkai

pada Trainer).

2. Ubahlah rangkaianHalfdanFull Adderhanya dengan gerbang NAND saja.

3. Ubahlah rangkaianHalfdanFull Subtractorhanya dengan gerbang NOR saja.

PERCOBAAN 8.Halaman 43RANGKAIAN ARITMETIKA DIGITAL DASAR